# DYNAMIC VIRTUAL CHANNEL NOC SYSTEM FOR GLOBALLY SYNCHRONOUS AND ASYNCHRONOUS ROUTER

Dr.G.Raja Kumar<sup>1</sup>, E.Princy<sup>2</sup>

<sup>1</sup>Associate Professor, Department of ECE & <sup>2</sup>PG Student,

Francis Xavier Engineering College, Vannarpettai, Tirunelveli-627003

#### **ABSTRACT:**

The approach for NOC topologies which is based on Router, synchronous memories and I/O Channel. Channel should be designed to comfortably handle the many-to-one data exchange and access data using routing controllers the existing system uses conventional channel dvnamic virtual architecture to handle traffic efficiently and it justifies the power consumption and speed performance improvement with row hit rate. But DVC method is compatible for either synchronous or asynchronous NOC, rather latest processors fabricated as Multi core. More data entry time and failed to describe bottleneck conditions. So we used dynamic VC approach. It enhances data access and overcome synchronization errors when compared to traditional solutions. Globally Synchronous and Asynchronous (GSAS) based Network on Chip optimizes memory and using thread row buffer. Our analysis takes place on a realistic NOC multimedia benchmark to prove large reduction in power consumption and improvement in performance and throughput

compared to existing solutions. It raises data flow and performance of the NoC system. Globally Synchronous and Asynchronous Memory controller for Dynamic Virtual Channel-NOC to avoid bottleneck traffic and multiple end to-end data flow between NOC soft-core processors with high data rate and low area consumption and Row Hit Distributed Arithmetic (RHDA) method is comprised to reduce latency.

*Key words*—VLSI based Network on chip, priority Scheduling, GSAS Router.

#### I. INTRODUCTION

Network on chip is a communication subsystem on an integrated circuit generally called as chip, frequently between intellectual property (IP) cores in a system on a chip. It can amount synchronous and asynchronous clock domains.conventional bus and crossbar intercon nections improves highly and it provide chip communication NoC improves the scalability of

System on chip, and the power ability of complicated System in Chip correlated to other designs. In Efficient Dynamic Virtual Channel Mechanism, It utilizes the common features of Dynamically Allocated Memory Queues input port to generate a dynamic flow control. Virtual Channel is used discharged with the flit-data in the input-port buffer to support the Efficient Dynamic Virtual Channel mechanism in circulating the request signals to the moderator. Virtual Channel -full and Virtual Channel -block signals are needed to sustain the order of flits correlate with each Virtual Channel. The flit arrival time and departure time entirely associated to a parallel FIFO. DVC method is suitable for either synchronous or asynchronous NOC, comparatively latest processors fabricated as Multi core. provide more data access time and failed characterizes bottleneck conditions It is used to process multi core functions and implement frequency synthesizer to hold multiple frequencies. To provide high speed data access between shared virtual memories a row hit protocol is introduced with Dynamic Virtual Channel Priority based data access with RHP Reduces traffic congestion and hardware overhead it is Compatible for multi-core processors without area overhead. It maintains Tradeoff between speed and QOS.

#### **II. Related Works**

In [1] An effective end-to-end flow control scheme, called Hotspot prevention is used to resolve the hotspot congestion problem for the Close network on the chip Specifically, HOPE regulates the injected traffic rate proactively by estimating the number of packets inside the switch network destined for each destination and applying a simple stop and-go protocol to prevent hotspot traffic from jamming the internal links of the network

.In [4] An efficient NoC design is used which is based on the transaction protocols used by onchip components.

In [5] A method for NoC topology generation and analysis is presented that incorporates onchip communication behavior and attempts to generate minimal topologies, both in terms of resource usage a Virtual channels are quintessential constructs in the correct operation of both the NoC routing algorithm and the CMP's cache coherence protocol. It introduces the notion of VC Renaming, which enables the further virtualization of existing VC buffers, in order to decouple the number of supported VCs in the system from the number of physically present VC buffers.

In [8] a new approach for implementing virtual channels (VC) for multi-core interconnection

networks is presented. Here the flits of different packets interleave in a channel with a single buffer of nominal depth by using a rotating flitby-flit arbitration.

In [18] Two new virtual channel allocation (VA) mechanisms, termed Fixed VC Assignment with Dynamic VC Allocation (FVADA) and Adjustable VC Assignment with Dynamic VC Allocation (AVADA) is presented. The idea is that VCs are assigned based on the designated output port of a packet to reduce the Head-of-Line (HoL) blocking

In [19] Multi-VC dynamically shared buffer named DAMQ-PF for network on chip to decrease the memory and area requirement of statically allocating shared buffer among multiple virtual channels (VC).

# III. PROPOSED SYSTEM

# A. Globally Synchronous And Asynchronous (GSAS) architecture

A GSAS approach is introduced to process multi core functions and implement frequency synthesizer to support multiple frequencies. To make high speed data access between shared virtual memories a row hit protocol is introduced with DVC (Dynamic Virtual Channel). Globally asynchronous locally synchronous (GALS) is a Model of Computation (MoC) that emerged in the 1980s. It is based on synchronous programming and asynchronous programming.

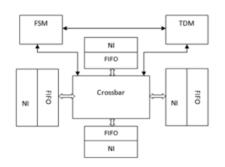

Fig1 Globally Synchronous and Asynchronous architecture

These changes are aggregated for synchronous circuit as most changes are initialized by an active clock edge. Therefore, large spikes on supply current A GALS circuit consist of a set of locally synchronous modules communicating with each other via asynchronous wrappers. Each synchronous subsystem ("clock domain") can run on its own independent clock (frequency). Advantages include much lower electromagnetic interference (EMI). The CMOS circuit (logic requires gates) relatively large supply current when changing occurs at active clock edges. These spikes can cause large electromagnetic interference, and may lead to circuit malfunction. In order to limit these spikes large number of decoupling

capacitors are used. Another solution is to use a GALS design style, i.e. design (locally) is synchronous but globally asynchronous, i.e. there are different (e.g. phase shifted, rising and falling active edge) clock signal regimes thus supply current spikes do not aggregate at the same time. Consequently, GALS design style is often used in system-on-a-chip (SoC).

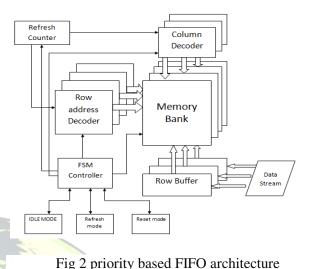

#### **B. Priority based FIFO architecture**

A priority queue is an abstract data type which is like a regular queue or stack data structure, but where additionally each element has a "priority" associated with it. In a priority queue, an element with high priority is served before an element with low priority. If two elements have the same priority, they are served according to their order in the queue. A priority queue is an abstract concept like "a <u>list</u>" or "a <u>map</u>"; just as a list can be implemented with a <u>linked list</u> or an <u>array</u>. priority queues typically O (log n) performance for inserts and removals, and O (n) to build initially. Variants of the basic heap data structure such as <u>pairing heaps</u> provide better bounds for some operation.

A priority queue must at least support the following operations:

insert with priority: add an element to the queue with an associated priority .pull highest Priority element: remove the element from the queue that has the highest priority, and return it

#### **PERFORMANCE ANALYSIS:**

#### **Throughput:**

It measures the total rate of data sent over the network, including the rate of data sent from source to router and data sent from node to destination

#### **Congestion control:**

In stack data Structure every element has a priority associated with it an element with high priority is served before an element with low priority hence it reduce traffic congestion

# **Delay:**

The delay of a network specifies how long it takes for a bit of data to travel across the network from one node or endpoint to another. it is typically measured in multiples or fractions of seconds.

#### **Overhead:**

Overhead is any combination of excess or indirect computation, time, memory, bandwidth or other resources that are required to attain a particular goal

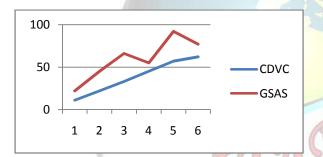

GSAS successfully brings out an improvement in latency by 45-50% and throughput by 70%.Time(s) is plotted along X axis and throughput is plotted along Y axis

# IV. CONCLUSIO AND FUTURE WORK: -

A Globally Synchronous and Asynchronous (GSAS) approach is introduced to process multi core functions and we implement frequency synthesizer to support multiple frequencies .To make high speed data access between shared virtual memories a Row Hit Distributed Arithmetic (RHDA) method is introduced with DVC (Dynamic Virtual Channel).where it is based on synchronous and asynchronous programming where is comprised to reduce latency. priority based data access with RHDA maintains tradeoff between speed and QOS .The proposed system reduces the hardware overheads and it become compatible for multi core processors without area overhead and finally it used all memory ports i.e. 100% efficiently

In future, re-organization of the existing single large row buffer in a DRAM bank into multiple smaller row-buffers. This configuration helps improve the row hit rates and also brings down the energy required for row-activations. The major contribution of this work is proposing such reorganization without requiring any significant changes to the existing widely accepted DRAM specifications.

# V. Reference

[1] N. Alfaraj, J. Zhang, Y. Xu, and H. J. Chao, "HOPE: Hotspot congestion control for Clos network on chip," in Proc. 5th IEEE/ACM NoCS, Pittsburgh, PA, USA, May 2011, pp. 17– 24

[2] Ashish Khodwe C. N. Bhoyar "Power and Area-Efficient Innovative Design of DynamicVirtual Channel For BiNoC Router" in

Priyadarshini college of Engineering , RTMNU, Nagpur, India,june 2010, pp99-121

[3] Chrysostomos A. Nicopoulos, Dongkook Park, Jongman Kim, N. Vijaykrishnan, Mazin S. Yousif †, Chita R. Das, "ViChaR: A Dynamic Virtual Channel Regulator for Network-on-Chip Router" The Pennsylvania state univ corporate Technology Group.intel group.University park,USA,Sept 2011,pp135-164

[4] V. Dumitriu and G. N. Khan, "Throughputoriented NoC topology generation and analysis for high performance SoCs," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 17, no. 10, pp. 1433–1446, Oct. 2009.

[5] M. Evripidou, C. Nicopoulos, V. Soteriou, and J. Kim, "Virtualizing virtual channels for increased network-on-chip robustness and upgradeability," in Proc. IEEE Comput. Soc. Annu. Symp. VLSI, Amherst, MA, USA, Aug. 2012, pp. 21–26.

[6] Jason Cong Michael Gill Yuchen Hao Glenn Reinman Bo Yuan, "On-chip Interconnection Network for Accelerator-Rich Architectures ,"in Center for Domain Specific Computing, UCLA,in vol22,pp341\_365

[7] M. O. Gharan and G. N. Khan, "Flexible simulation and modeling for 2D topology NoC system design," in Proc. 24th CECE, Niagara

Falls, ON, Canada, May 2011, pp. 000180–000185

[8] M. O. Gharan and G. N. Khan, "A novel virtual channel implementation technique for multi-core on-chip communication," in Proc. WAMCA, New York, NY, USA, 2012, pp. 36–41A.

[9] P. Gratz, B. Grot, and S.W. Keckler. "Regional congestion awareness for load balance in network-on-chip." In HPCA, Feb. 2008

[10] K. Kodi, A. Sarathy, Vivek Venkatesan and A. Louri, "iDeal: Inter-router dual-function energy and area-efficient links for network-onchip (NoC) architectures," International Symposium on Computer Architecture, pp. 241-250, 2008.

[11] A.Kumar, L.-S. Peh, P. Kundu and N.K. Jha, "A 4.6 Tbits/s 3.6GHz single-cycle NoC router with a novel switch allocator in 65nm CMOS," International Conference on Computer Design, pp.63-70, 2007

[12] Pascal Vivet, Didier Lattard, Fabien Clermidy, Edith Beigne, Christian Bernard, Yves Durand, Jean Durupt, Didier Varreau," FAUST an Asynchronous Network-on-Chip based Architecture for Telecom Applications." in CEA-LETI, MINATEC, 38054 Grenoble, FRANCE, pp157-202,2009

[13] Robert Mullins, Andrew West and Simon

"Moore Low-Latency Virtual-Channel Routers for On-Chip Networks." in Computer

Laboratory, University of Cambridge William.

Gates Building, JJ Thomson Avenue,

Cambridge CB3 0FD, UK, pp89-96, 2008

[14] Rostislav (Reuven) Dobkin, Ran Ginosar and Israel Cidon QNoC "Asynchronous Router with Dynamic Virtual Channel Allocation."in VLSI Research Technology –Israel Institute of technology,Haifa 32000,Israel,pp 341-355,2009

[15] Salman Onsori, Farshad Safaei "Performance Enhancement of Routers in Networks-on-Chip Using Dynamic Virtual Channels Allocation" Shahid Beheshti University G.C., Evin 1983963113, Tehran, IRAN,pp111-125,Jan 2005

[16] Sung-Tze Wu, Chih-Hao Chao, I-Chyn Wey, and An-Yeu (Andy) Wu"Dynamic Channel Flow Control of Networks-on-Chip Systems for High Buffer Efficiency"in Institute of Electronics Engineering and Department of Electrical Engineering National Taiwan University pp. 667-672, Jun. 2001.

[17] Victor Goulart "Performance of Low Buffer Resource Flexible Router for NoCs" E- JUST Center, Kyushu University Fukuoka, Japan,pp121-142,2007

[18] Y. Xu, B. Zhao, Y. Zhang, and J. Yang, "Simple virtual channel allocation for high throughput and high frequency on-chip routers," in Proc. IEEE 16th Int. Symp. High Perform.